# Design and Simulation of Nonisolated ZVZCS Resonant PWM Converter for High Step-Up and High Power Applications

# S.M.MohamedSaleem,K.KalaiRaja<sup>1</sup>,A.MohamedIlyasMydeen<sup>2</sup>,C.R.Mohan Raj <sup>3</sup>.M.Hazina<sup>4</sup>

<sup>1</sup>UG Scholars, \*\*Asst. professor, Syed Ammal Engineering College, Ramanathapuram Tamil Nadu, India

# ABSTRACT

This paper proposes a generalized scheme of new soft-switched interleaved boost converters that is suitable for high step-up and high power applications. The proposed converter is configured with proper numbers of series and parallel connected basic cells in order to fulfill the required output voltage and power levels respectively. This leads to flexibility in device selection resulting in high component availability and easy thermal distribution. Design examples of determining the optimum circuit configuration for given output voltage gain of 8.75times is presented.

KEY WORDS: High Step-Up, High Voltage Gain, Multiphase, Non-isolated, Soft Switched.

# I. INTRODUCTION

Recently, high step-up dc-dc converters do not require isolation have been used in many applications such as dc back-up energy systems for Uninterruptible Power Systems(UPS), renewable energy systems, fuel cell systems and hybrid electric vehicles. Generally, the high step-up dc-dc converter for these applications has the following requirements.

- [1] High step-up voltage gain. Sometimes the voltage gain could be more than 10.

- [2] High current handling capability.

- [3] High efficiency at a desired level of volume and weight.

- [4] Low input current ripple.

In order to provide high output voltage, the classical boost converter should operate at extremely duty cycle and then the rectifier diode must sustain a short pulse current with high amplitude. This results in severe reverse recovery as well as high EMI problems. Using an extremely duty cycle may also lead to poor dynamic responses to line to load variations. Moreover, in the high step up dc-dc converter the input current is usually large, and hence low voltage rated MOSFETs with small RDS(ON) are necessary in order to reduce the dominating conduction loss. However, the switch in the classical boost converter should sustain high output voltage as well, and therefore, the device selection is faced with a contradiction. A lot of step-up dc-dc converter topologies have been presented to overcome the aforementioned problem. Converters with Coupled inductors [1]-[5] can provide high output voltage without using high duty cycle and yet reduce the switch voltage stress. The reverse recovery problem associated with rectifier diode is also alleviated. However, they have large input current ripple and are not suitable for high power applications since the capacity of the magnetic core is considerable. The switched-capacitor converter [6]-[10] does not employ an inductor making it feasible to achieve high power density. However, the efficiency could be reduced to allow output voltage regulation. The major drawback of these topologies is that attainable voltage gains and power levels without degrading system performances are restricted.Most of the coupled-inductor and switched-capacitor converters are hard switched and therefore, they are not suitable for high efficiency and high power applications. Some soft switched interleaved high step-up converter topologies [11]-[ 18] have been proposed to achieve high efficiency at desired level of voltage and power level.

In this paper, a new interleaved soft switched high step-up dc-dc converter for high efficiency, high voltage applications are presented. The proposed converter has the following advantages.

- [1] Reduced voltage stresses of switches and diodes,

- [2] ZVS turn-on the switches and ZCS turn-off the diodes.

- [3] Low input current ripple due to interleaved structure.

- [4] Reduced energy volumes of most passive components.

- [5] Extendibility to desired voltage gain and power level.

www.ijceronline.com

||May ||2013||

The operating principles alog with a design example of the proposed converter are described. Experimental results from a 1.5-KW prototype are also provided to validate the proposed concept.

### PROPOSED INTERLEAVED HIGH STEP-UP CONVERTER

2.1.General Architecture

II.

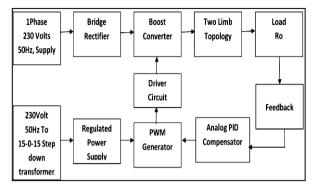

**Fig. 1. General Architecture** *Fig. 1. Block diagram of general architecture*

Architecture Description

Fig.1 shows the Architecture of the proposed converter. The single phase AC supply is converted into DC supply and applied to boost converter. Due to two limb topology the output power is greatly increased compared to that of conventional converter. The switch is controlled by means of PWM technique. Hence controlled DC voltage is applied to the DC Load.

#### **B. GENERALIZED MULTIPHASE DC-DC CONVERTER**

Fig. 2 shows a basic cell used as a building block to build the proposed high step-up converter. The basic cell consists of an input filter inductor, a switch leg and diode leg, and an auxiliary inductor, and capacitor.

$\begin{array}{c|c} S_{U} \\ & D_{U} \\ \hline \\ & C_{2} \\ & C_{2} \\ & C_{2} \\ \hline \\ & C_{2} \\ & C_{$

Fig. 2 Basic cell of the proposed interleaving high step-up converter.

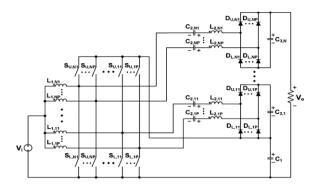

Fig. 3 shows the generalized circuit of the proposed converter with N and P, where N is the number of output series-connected basic cell and P is the number of output parallel-connected basic cell, respectively, meaning that there exist totally N.P basic cells. The diode leg of npth basic cell is connected to the output capacitor C3,n, where n=1,2,3,...,N and p=1,2,3,...,P, and output capacitors C3,1 to C3,N are connected in series on top of output capacitor C1 to form the output voltage. That is, "N" could be increased to get higher output power. It should be noted that the voltage rating of switches can be reduced by reducing N and the current rating of them can be reduced by increasing N or P. Also, the voltage and current ratings of diodes can be reduced proper choice of N&P. The interleaving technique can be applied to reduce the size of input filter inductors and output filter capacitors. Therefore, "N"and "P" can properly be chosen according to given output voltage and power level. This could give flexibility in device selection resulting in optimized design even under harsh design specifications.

*Fig. 3. Generalized circuit topology of the proposed interleaved high step-up dc–dc converter (N is the number of output series-connected basic cell, and P is the number of the output parallel-connected basic cell).*

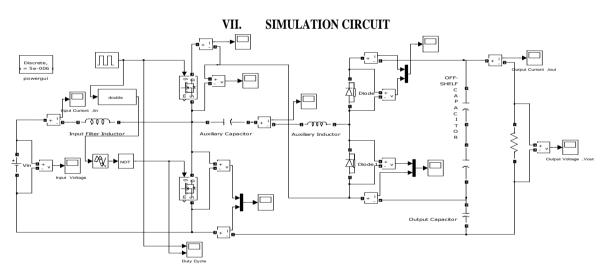

#### III. CIRCUIT DIAGRAM

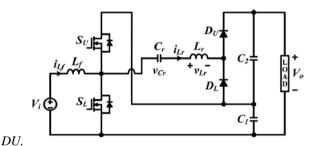

Fig. 4.shows the circuit diagram of the proposed converter which has the same circuit topology as the PWM method proposed in [14]. Fig.5. shows key waveforms illustrating the operating principle of the proposed converter .The proposed converter consists of a general boost converter as the main circuit and an auxiliary circuit which includes capacitor *Cr*, inductor *Lr* and two diodes *DL* and

Fig.4.Circuit diagram of the Proposed Converter

Two switches are operated with asymmetrical complementaryswitching to regulate the output voltage. Owing to the auxiliary circuit, not only output voltage is raised but ZVS turn-on of two switches can naturally be achieved in CCM by using energy stored in filter inductor Lf and auxiliary inductor Lr. Unlike PWM method [14] in which the switches are turned OFF with high peak current the proposed converter utilizes Lr-Crresonance of auxiliary circuit, thereby reducing the turn-off current of switches. Futhermore, for resonance operation, the capacitance of Cr is reduced volume. Also, switching losses associated with diode reverse recovery of the proposed RPWM converter are significantly reduced.

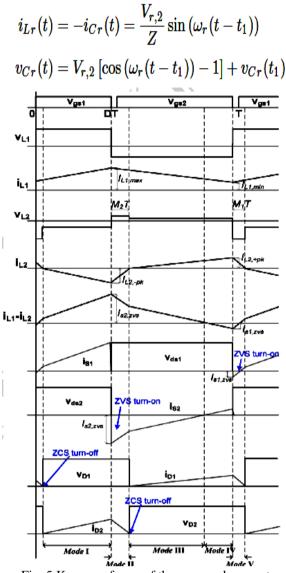

## IV. OPERATING PRINCIPLE

The operating modes and key waveforms of the proposed converter are shown in Figs. 5 and 6. In the below resonance operation, five modes exist within *Ts. Mode 1* ( $t_0 - t_1$ ): This mode begins when upper switch  $S_U$  which was carrying the current of difference between  $i_{Lf}$  and  $i_{Lr}$  is turned OFF.  $S_L$  can be turned ON with ZVS if gate signal for  $S_L$  is applied before the current direction of  $S_L$  is reversed. Filter inductor current  $i_{Lf}$  and auxiliary current  $i_{Lr}$  starts to linearly increase and decrease, respectively, as follows

$$egin{aligned} &i_{Lf}(t) = rac{V_i}{L_f}(t-t_0) + i_{Lf}(t_0) \ &i_{Lr}(t) = rac{V_{Cr,\min} - V_o}{L_r}(t-t_0) + i_{Lr}(t_0) \end{aligned}$$

This mode ends when decreasing current  $i_{Lr}$  changes its direction of flow. Then  $D_U$  is turned OFF under ZCS condition.

*Mode* 2  $(t_1-t_2)$ : This mode begins with  $L_r-C_r$  resonance of the auxiliary circuit. Current  $i_{Lf}$  is still linearly increasing. The voltage and current of resonant components are determined, respectively, as follows:

Fig. 5.Key waveforms of the proposed converter

Where  $V_{r,2} = V_{Cr,min} - V_{CI}$ ,  $Z = \sqrt{L_r/C_r}$  and  $\omega_r = 1/\sqrt{L_r/C_r}$ . The resonance mode ends when  $i_{Lr}$  reaches to zero. Note that  $D_L$  is turned OFF under ZCS condition.

*Mode* 3  $(t_2 - t_3)$ : There is no current path through the auxiliary circuit during this mode. Output capacitors supply the load. At the end of this modethe turn-off signal of  $S_L$  is applied. It is noted that the turn-off current of  $S_L$ ,  $I_{SL,off}$  is limited to filter inductor current at  $t_3$ ,  $I_{Lf,max}$ , which is much smaller than that of PWM method.

*Mode*  $4(t_3 - t_4)$ : This mode begins when lower switch  $S_L$  is turned OFF.  $S_U$  can be turned ON with ZVS if gate signal for  $S_U$  is applied before the current direction of  $S_U$  is reversed. Filter inductor current  $i_{L_f}$  starts to linearly decrease since voltage  $V_{L_f}$  becomes negative

$$i_{Lf}(t) = rac{V_i - V_{C1}}{L_f}(t-t_3) + i_{Lf}(t_3).$$

Like Mode 2, the other  $L_r$ - $C_r$  resonance of auxiliary circuit is started, and  $D_U$  starts conducting. The voltage and current of resonant components are determined, respectively, as follows:

$$egin{aligned} &i_{Lr}(t) = -i_{Cr}(t) = rac{V_{r,4}}{Z} \sin{(\omega_r(t-t_3))} \ &v_{Cr}(t) = V_{r,4} \left[\cos{(\omega_r(t-t_3))} - 1

ight] + v_{Cr}(t_3) \end{aligned}$$

where  $V_{r,4} = V_{Cr,max} - V_{C2}$ ,  $Z = \sqrt{L_r/C_r}$  and  $\omega_r = 1/\sqrt{L_r/C_r}$ .

This mode ends when  $i_{Lr}$  is equal to  $i_{Lf}$ .

*Mode* 5  $(t_4 - t_5)$ : After  $i_{Lr}$  equals  $i_{Lf}$ ,  $i_{SU}$  changes its direction, then this mode begins. At the end of this mode, turn-off signal of  $S_U$  is applied and this mode ends.

#### V. VOLTAGE CONVERSION RATIO

To obtain the voltage gain of the proposed converter, it is assumed that the voltage across  $C_1$  and  $C_2$  are constant during the switching period  $T_s$ . The output voltage is given by

$$V_o = V_{C1} + V_{C2}$$

$$V_o = rac{2}{1-D_{ ext{eff}}} V_i = rac{2}{1-D} V_i - \Delta V \, .$$

It can also be expressed as

effective duty  $D_{eff}$  and voltage drop  $\Delta V$  are expressed using duty loss  $\Delta D$ .

$$egin{aligned} D_{ ext{eff}} &= D - \Delta D \ \Delta V &= rac{2\Delta D V_i}{(1-D)(1-D_{ ext{eff}})} \end{aligned}$$

$V_{C1}$  that is the same as output voltage of the boostconverter

where

$$V_{C1} = \frac{1}{1-D} \cdot V_i.$$

4

can be expressed as

Design is carried out for findingLf, fr,Lr and Cr A. Design of Lf  $V_{C2}$  can be expressed as

$$V_{C2}=rac{1}{1-D}V_i-\Delta V.$$

In the steady state, the average load current equals the average current of diodes  $D_L$  and  $D_U$ . Since  $i_{Lr}$ , flows through the  $D_L$  during mode 2, the average load current can be obtained as follows.

$$I_{\rm DL,av} = \frac{V_o}{R_o} = \left| \frac{2}{T_s} \int_0^{T_r/4} (V_{Cr,\min} - V_{C1}) \frac{\sqrt{C_r}}{\sqrt{L_r}} \sin(\omega_r t) \cdot dt \right|$$

From the above equation,  $V_{Cr,min}$  and  $V_{Cr,max}$  can be obtained by,

$$V_{Cr,\min} pprox V_{C1} - rac{V_o}{2C_r R_o f_s}$$

$V_{Cr,\max} pprox V_{C1} + rac{V_o}{2C_r R_o f_s}.$

## VI. DESIGN OF THE PROPOSED CONVERTER

The generalized scheme of the proposed converter has been shown in Fig.3.,where it is configured with proper numbers of series and parallel connected basic cells. This leads to flexibility in device selection resulting

in high-component availability and easy thermal distribution. A specification for a design example in this paper is given as follows and the chosen circuit topology for the specifications is shown in Fig.4.

Po = 220 W, Vo = 105 V, Vi = 12 V, fs = 15 kHz,  $\Delta Iin = 20\%$ ,  $\Delta Vo = 3\%$ . Considering input current ripple  $\Delta I_{in}$  input inductor  $L_f$  is determined by,

Lf = 0.5(1-D).  $V_{in}/\Delta I_{in}$ .  $f_s = 70\mu$ H.

#### **B.** Design of $f_r$

Due to the smaller switch turn off current and duty loss, the below-resonance operation is chosen, and the resonant frequency  $f_r$  can be obtained from

$f_r = 1 / 2\pi \sqrt{L_r C_r}$  and  $f_r = 1 / 2D_{eff.}$

So,  $f_r \le 42 \text{ kHz}$

C. Design of  $L_r$  and  $C_r$

From the resonant frequency  $f_{r_i}$

$L_r = 3 \ \mu H \&$

$C_r = 4.7 \ \mu F.$

The improvement of the proposed RPWM method compared to PWM method are summarized as follows.

1) Due to the reduced operation duty, the rms current ratings of the switches are reduced by 5-15%, resulting in reduced conduction losses.

2)Due to the resonant operation, the turn-off current of switches are reduced by 25-60% and falling slopes of the diode current are reduced, resulting in significantly reduced switching losses.

3)The required capacitance of auxiliary capacitor is dramatically reduced to 1/20<sup>th</sup> resulting in reduced volume and cost.

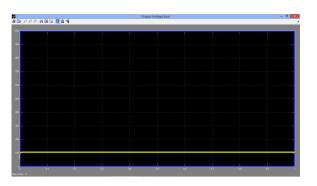

Fig(a) Input voltage

Fig(b) Output voltage

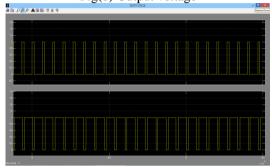

Fig(c)Duty cycle

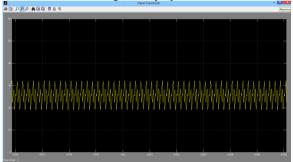

Fig(d) Input current

Fig(e) Output current

# V. CONCLUSION

In this paper, an RPWM method switching method has been proposed for high step-up soft switching dc-dc converter. The proposed converter has the following advantages:

- The proposed converter has the following advantages:

- a. ZVS turn-on of the active switches in CCM.

- b. Negligible diode reverses recovery due to ZCS turn-off of the diodes.

- c. Greatly reduced passive components and voltage ratings.

- d. Its voltage gain is 8.75 times, is doubled with the classical boost converter.

#### REFERENCES

- [1] K. Hirachi, M. Yamanaka, K. Kajiyama, and S. Isokane, "Circuit configuration of bidirectional DC/DC converter specific for small scale load leveling system," in Proc. IEE Power Conv. Conf., Apr. 2002, vol. 2, pp. 603-609.

- [2] Q. Zhao and F. C. Lee, "High-efficiency, high step-up DC-DC converters," IEEE Trans. Power Electron., vol. 18, no. 1, pp. 65–73, Jan.2003.

- T. J. Liang and K. C. Tseng, "Analysis of integrated boost-flyback step-up converter," in Proc. IEE Electr. Power [3] Appl., Mar. 2005, vol. 152, no. 2, pp. 217–225.

- [4] R. J. Wai and R. Y. Duan, "High-efficiency DC/DC converter with high voltage gain," in Proc. IEE Electr. [4] Power Appl., Jul. 2005, vol. 152, no. 4, pp. 793-802.

- B. Axelrod, Y. Berkovich, and A. Ioinovici, "Switched coupled-inductor cell for DC-DC converters with very [5] large conversion ratio," IEEE Int. Conf. (IECON), pp. 2366-2371, Nov. 2006.

- M. S. Makowski, "Realizability conditions and bounds on synthesis of switched-capacitor dc-dc voltage multiplier [6] circuits," IEEE Trans. Circuits

- Syst. I. Fundam. Theory Appl., vol. 44, no. 8, pp. 684–691, Aug. 1997. [7]

- [8] O. C.Mak,Y. C.Wong, andA. Ioinovici, "Step-upDC power supply based on a switched-capacitor circuit," IEEE Trans. Ind. Electron., vol. 42, no. 1, pp. 90-97, Feb. 1995.

- O. Abutbul, A. Gherlitz, Y. Berkovich, and A. Ioinovici, "Step-up switching-mode converter with high voltage [9] gain using a switchedcapacitor circuit," IEEE Trans. Circuits Syst.-I, vol. 50, no. 8, pp. 1098-1102, Aug. 2003.

- B. Axelrod, Y. Berkovich, and A. Ioinovici, "Transformerless DC-DC converterswith a very highDCline-to-load [10] voltage ratio," in Proc. Circuits Syst., Int. Symp. Circuits Syst. (ISCAS), May 2003, vol. 3, pp. III435- III438.

- [11] B. Axelrod, Y. Berkovich, and A. Ioinovici, "Switched-capacitor/switched-inductor structures for getting transformerless hybrid DC-DC PWM converters," IEEE Trans. Circuits Syst. I: Regul. Paper, vol. 55, no. 2, pp. 687-696. Mar. 2008.

- [12] E. H. Ismail, M. A. Al-Saffar, A. J. Sabzali, and A. A. Fardoun, "A family of single-switch PWM converters with high step-up conversion ratio,"IEEE Trans. Circuits Syst. I: Regul. Paper, vol. 55, no. 4, pp. 1159-1171, May 2008

- R. Giral, L. S. Martinez, and S. Singer, "Interleaved converters operation basedonCMC," IEEE Trans. Power [13] Electron., vol. 14, no. 4, pp. 643-652, Jul. 1999.

- P. W. Lee, Y. S. Lee, D. K. Cheng, and X. C. Liu, "Steady-state analysis of an interleaved boost converter with [14] coupled inductors," IEEE Trans. Ind. Electron., vol. 47, no. 4, pp. 787-795, Aug. 2000.

- B. Huang, I. Sadli, J. P. Martin, and B. Davat, "Design of a high power, high step-up non-isolated DC-DC [15] converter for fuel cell applications," IEEE Vehicle Power Propulsion Conf. (VPPC), pp. 1-6, Sep. 2006.

- L. Palma, M. H. Todorovic, and P. Enjeti, "A high gain transformer-less DC-DC converter for fuel-cell [16] applications," IEEE Power Electron.Spec.Conf. (PESC), pp. 2514-2520, Jun. 2005.

- [17] D. Coutellier, V. G. Agelidis, and S. Choi, "Experimental verification of floating-output interleaved-input DC-DC high-gain transformer-less converter topologies," IEEE Power Electron. Spec. Conf. (PESC), pp. 562-568, Jun. 2008.

- R. N. A. L. Silva, G. A. L. Henn, P. P. Prac, a, L. H. S. C. Barreto, D. S. Oliveira, Jr., and F. L. M. Antunes, "Soft-[18] switching interleaved boost converter with high voltage gain," IEEE Power Electron. Spec. Conf. (PESC), pp. 4157-4161, Jun. 2008.

- [19] W. Li and X. He, "High step-up soft switching interleaved boost converters with cross-winding-coupled inductors and reduced auxiliary switch number," *IET Power Electron.*, vol. 2, no. 2, pp. 125–133, Mar. 2009. S. Park and S. Choi, "Soft-switched CCM boost converters with high voltage gain for high-power applications,"

- [20] IEEE Trans. Power Electron., vol. 25, no. 5, pp. 1211–1217, May 2010.

- [21] Dinesh K" Analysis of Multiphase Boost Converter for High Power Application" International Journal of Applied Information Systems (IJAIS) - ISSN: 2249-0868 Foundation of Computer Science FCS, New York, USA Volume 1-No.7, March 2012.

- R.Saktheeswaran, S.Sulthansikkanderbadusha, A.Parthiban, "High-Power Applications CCM Boost Converter [22] with Two Limb Topology Using Soft-Switching Techniques" International Journal of Engineering Research and Applications (IJERA) ISSN: 2248-9622 Vol. 3, Issue 2, March - April 2013, pp. 1752-1756.

- Ganga jeyadevi.R, low loss soft-switching boost converter with hi-bridge auxiliary [23] resonant circuit. International Journal of Communications and Engineering Volume 04–No.4, Issue: 02 March2012.

- [24] C.Benin, Dr.M.Sasikumar," Simulation And Analysis Of Soft-switching Ccm Boost Converter With High Power Applications "IOSR Journal of Engineering (IOSRJEN), Vol. 2 Issue 2, Feb. 2012, pp. 203-206.

## ACKNOWLEDGEMENT

**Mohamed Saleem. S.M.** is currently pursuing the B.E Degree in Electrical and Electronics Engineering from Syed Ammal Engineering College, Anna University, Chennai, India. His current research interests include design and implementation of new interleaved soft switching boost converter with high step-up applications.

**KalaiRaja.K** are currently pursuing the B.E Degree in Electrical and Electronics Engineering from Syed Ammal Engineering College, Anna University, Chennai, India. His current research interests include design and implementation of new interleaved soft switching boost converter with high step-up applications.

**Mohamed Ilyas Mydeen.A** are currently pursuing the B.E Degree in Electrical and Electronics Engineering from Syed Ammal Engineering College, Anna University, Chennai, India. His current research interests include design and implementation of new interleaved soft switching boost converter with high step-up applications.

**MohanRaj.C.R.** are currently pursuing the B.E Degree in Electrical and Electronics Engineering from Syed Ammal Engineering College, Anna University, Chennai, India. His current research interests include design and implementation of new interleaved soft switching boost converter with high step-up applications.

**Hazina.M** received the B.E degree from Anna University Chennai in 2010 and M.E degree from the same university in2012.She is currently working as a assistant professor in Syed Ammal Engineering College,Ramanathapuram,Tamilnadu,India. Her current research interests include design and implementation of new interleaved soft switching boost converter with high step-up applications.